猜你喜欢

传统的CMOS技术通过工艺微缩来提供更好的器件性能和更高的元件密度,从而在更低的成本下获得更好的系统性能。然而,随着工艺的不断微缩,传统的金属氧化物半导体场效应晶体管结构正受到一些基本要求的限制,它所要求的更薄栅氧化物和更高的沟道掺杂会使得器件产生高漏电和低性能。所以,需要通过新技术与迁移速率提升 工艺来维持CMOS器件的微缩路线图 。高介电常数栅氧化物和金属栅电极工艺已经在第4章中讨论,本章将讨论一种提升迁移速率的工艺方法,即局部应力工艺。

应用于单晶硅上的机械应力将会改变原子内部的晶格间距,相应地改变了电子能带结构和密度,从而改变载流子的迁移率。载流子的迁移率为

(5-2)

由此可见,增加载流子的迁移率可以增加它的速度,从而直接增加器件的驱动电流。应力对器件的驱动电流的影响与单晶硅基体的沟道方向有密切关系。文献[3]讨论了它们在今天集成电路工业中起主导材质的(100)晶面单晶硅上的相关性,如图5.1所示。

图5.1 沟道晶向和应力类型对于CMOS器件驱动电流的影响

从图5.1中可以看出,当拉应力作用于<110>和<100>晶向沟道上时,NMOS器件的驱动电流都会随应力增加而增加。而压应力作用于其上时,它的驱动电流会随应力增加而减少。PMOS器件的行为和NMOS器件是不同的,不管是拉应力还是压应力,几乎不会影响<100 >沟道的PMOS器件驱动电流。

为了获得应变工程的好处,PMOS器件 需要做在<110>沟道上。作用于<110>沟道上的压应力正比于 PMOS器件的驱动电流的大小;而拉应力则反之,越大的拉应力获得的驱动电流越小。需要指出的是,没有受到应变作用的PMOS器件在 <100>沟道上的驱动电流大于<110>沟道,这就是为什么有些公司 在90nm和65nm工艺中PMOS没有使用应变硅迁移率提升技术的时候, 采用<100>晶向的单晶硅(100)晶面衬底的原因。

图5.1已经总结了集成电路工业中广泛使用的驱动电流与应力和沟道方向的相关性及其提升CMOS器件性能的方法。在本章中,我们将讲解一些主要的应变工程技术。5.2节中将讨论源漏区嵌入技术,源漏 区嵌入式锗硅技术产生的压应力已经被证明可以有效提高PMOS器件的驱动电流(详见5.2.1节)。另外一方面,源漏区嵌入式碳硅技术产生的拉应力可以提高NMOS器件的驱动电流(详见5.2.2节)。5.3节将讨论在NMOS器件性能提升中广泛使用的应力记忆技术,5.4节将讨论金属前通孔双极应力刻蚀阻挡层技术,拉应力可以提高NMOS的器件性能,而压应力可以提高PMOS的器件性能。最后一节将讨论应变效果提升的技术,包括应力临近技术和可替代栅提高应变的技术等。

5.2 源漏区嵌入技术5.2.1 嵌入式锗硅工艺嵌入式锗硅工艺(embedded SiGe process)被广泛使用于90nm及以下技术中的应力工程,利用锗、硅晶格常数的不同所产生的压应力 (compressive stress),嵌入在源漏区,提高PMOS空穴的迁移率和饱和电流。硅的晶格常数是5.43095Å,锗的晶格常数是5.6533Å,硅与锗的不匹配率是4.1%,从而使得锗硅的晶格常数大于纯硅,在源漏区产生压应力。

锗硅工艺有选择性锗硅和不选择性锗硅两种。CMOS工艺流程中的嵌入式锗硅使用选择性锗硅工艺。在进行选择性锗硅工艺前,对NMOS的地方需要采用氧化物或氮化物的保护层,然后在显影后,对PMOS进行硅衬底的刻蚀和残留聚合物的去除。

选择性锗硅外延薄膜需要采用的分析仪器包含:

XRD用于厚度和浓度的离线测定Auger/SIMS用于浓度和深度分布的测定SEM用于 轮廓和形态的查看(profile and morphology top view)TEM用于轮廓 和晶格缺陷的查看(profile and dislocation defects)光学颗粒测定仪 ( particle count ) 用于在线微粒和haze的标定椭圆偏振仪 (spectroscopic ellipsometry)用于锗硅厚度和锗含量的在线检测另外可以采用拉曼(Raman)光谱的方法测定应力。

选择性锗硅工艺可以分为两种工艺流程,一种是在形成侧墙offset工艺之前嵌入锗硅(SiGe first process),另一种是在源漏扩展区和侧墙工艺形成后嵌入锗硅(SiGe last process),如图5.2所示

图5.4 阶梯式的选择性锗硅外延工艺示意图

选择性锗硅工艺还需要处理不同版图的差异问题,同样的程式, 在硅凹穴多的产品上会获得更低的浓度和更慢的生长速率。而在微观上,还需要处理不同区域的微观差异问题(micro-loading),特别是在SRAM和逻辑区域。如图5.5所示,区域的微差异对生长速率和锗含量均有明显影响。

图5.7 通过多次沉积和刻蚀循环来获得嵌入式碳硅薄膜

化学气相沉积形成的嵌入式碳硅工艺在原位N型原子掺杂上也有优势,比如磷的掺杂。文献[16] 报道了一个成功的例子,使用原位磷掺杂碳硅工艺来提高NMOS器件的性能(见图5.8)。它也说明了碳硅工艺在未来持续微缩的器件上面所具有的优势。

图5.8 参考文献[6] 报道的I on-I off 曲线显示出了嵌入式碳硅工艺在提高NMOS器件驱动电流上面的好处

嵌入式碳硅工艺除了在源漏区制造的困难外,如何在后续的工艺步骤中把所掺入的碳保持在替位晶格中也是一个巨大的挑战。一旦碳原子不在替位晶格中,那么应变效果就失去了。图5.9给我们展示了应变和退火温度的关系,当外延碳化硅遇到后续的高温退火时,巨大数目的碳原子离开了原来替位晶格的位置,特别是高浓度的碳硅薄膜。 在990℃的尖峰退火工艺后,掺杂2.2%和1.7%原子的碳化硅薄膜将失去约30%的应变,而掺杂1%原子的碳化硅薄膜将失去约10%的应变。 所以,外延碳硅薄膜形成后的热预算需要进行很好的控制,以利于应变效果的保持。由于毫秒退火工艺具有更快的升温和降温速率,把它应用在外延碳化硅薄膜形成后的热工艺中,可以获得一些好处 。 本书第10章将详细讨论毫秒退火工艺。

图5.9 外延碳硅形成后的尖峰退火工艺对替位晶格碳原子数目的影响

5.3 应力记忆技术应力记忆技术(Stress Memorization Technique,SMT),是90nm 技术节点以下兴起的一种着眼于提升NMOS器件速度的应力工程。SMT的特点在于,该技术凭借拉应力作用,可以显著加快NMOS器件的电子迁移率,从而提高NMOS器件的驱动电流;然而,SMT在集成电路制造技术中如同一个“隐形人”,在整个工艺流程完成之后,该项技术不会对器件产生任何结构性的变化。

5.3.1 SMT技术的分类在业界早期的探索中,SMT出现了许多流派:

(1)源、漏极离子注入完成之后,采用低应力水平的膜层(如二氧化硅)作为保护层,对多晶硅栅极进行高温退火

(2)源、漏极离子注入完成之后,采用高应力水平的膜层(如高应力氮化硅)作为保护层,再对多晶硅栅极进行高温退火 ;

(3)沉积高应力水平的膜层之后,直接做高温退火,而不采用预先的离子注入非晶化过程。

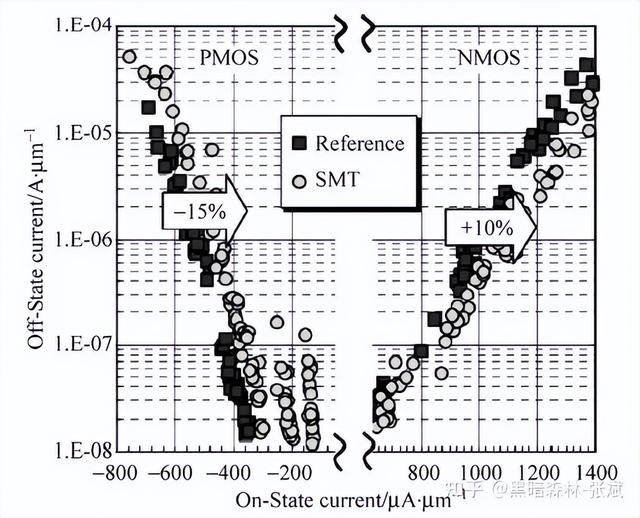

在这三大流派下面,还有很多具体的分支,诸如离子注入的条件差异、应力膜系的选择、退火条件的不同等。随着研究的逐步深入以及工业应用的反馈,上述第二种流派被越来越多的业者青睐,已经成为SMT的主流技术。而事实上,在这一分支下,仍有许多探索和实验在进行。有研究表明传统的SMT技术会降低PMOS器件的驱动电流,如图5.10所示,NMOS速度可以提高10%以上,而PMOS却有15%的衰减。

那么如何解决SMT的这种负面效应呢?研究者再次给出了不同的答案:比较传统的思路是,在完成高应力膜层(通常是氮化硅)沉积之后,额外增加一层光刻和刻蚀,去除PMOS区域的薄膜,再进行高温退火。但这种方法会消耗更多的制造成本,而且引入多一层光刻和刻蚀,也会给工艺控制带来更多的变异,因此有学者提出通过改善 应力膜层自身特性的方法,达到既可以提高NMOS的器件速度,又不损伤PMOS性能。

需要说明的是,由于NH3 比 N2 更易于解离,所以式(5-3)的反 应中,大部分N离子来源于 NH3 ,N2 主要起稀释和平衡气压的作用, 但也会参与反应。式(5-4)的反应则不采用NH3 ,直接用N2 提供N离 子,反应速度会相应降低。不论是哪种反应制备的氮化硅,其中除了Si原子和N原子之外,还有含量不等的H原子,主要以Si-H,N-H的形 式存在。H原子的含量及存在方式,对氮化硅薄膜的致密度、折射 率、应力大小有极大影响。H离子的来源有两个:SiH4 和 NH3 ,所以 即便是式(5-4)的反应也无法制备不含H的氮化硅。人们可以根据器 件特性的需要,通过变化工艺参数来调整H原子含量,从而得到理想 性能的氮化硅薄膜。反应温度,气体流量,射频电源频率和功率,反应气压等都可以影响氮化硅中H原子含量及其性质。一般来说, (SiH4 NH3)/N2 比例越大,高频电源(13.3MHz)功率越大,反应 温度越低,H含量越高,本征应力越低(有时也叫沉积应力)。

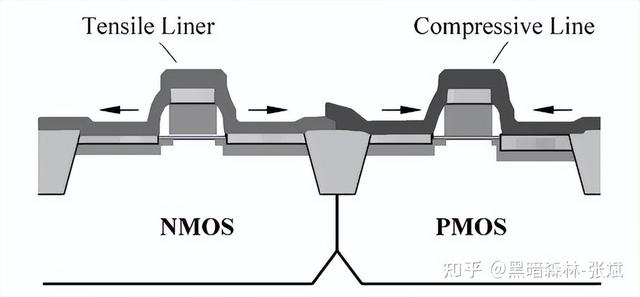

5.4 双极应力刻蚀阻挡层我们在5.1节中曾提到,对于硅衬底为(100)晶面的半导体器件,应力加载于载流子隧道,可对器件驱动电流产生极大的影响。对于NMOS器件而言,拉应力可以显著提升<110>和<100>晶向沟道的电子迁移率;而压应力则只对<110>晶向的空穴起作用,对于< 100>晶向沟道的空穴作用可以忽略不计。在CMOS工艺流程中,通常 会采用一种有等离子增强化学气相沉积生长的氮化硅,作为半导体器件和后段互连线之间的金属前通孔(contact)的刻蚀阻挡层。随着半导体器件工艺的发展,对于器件工作速率的要求越来越高,这一道刻蚀阻挡层被赋予了更多的使命,可以通过沉积工艺和沉积后处理来调整其薄膜应力,从而对NMOS和PMOS器件均产生积极影响。

对于65nm节点之前的器件来说,通常只采用一道拉应力氮化硅作为刻蚀阻挡层,可以提升(100)晶面硅衬底上<100>晶向的NMOS 的电子迁移率,且对PMOS没有负面作用。当半导体工艺发展到45nm 节点以下时,如何加大PMOS的载流子速度逐渐被提上日程,在这种情况下,业界先驱者开发出双极应力刻蚀阻挡层,通过采用压 应力氮化硅来提升(100)晶面硅衬底上<110>晶向的PMOS器件的空穴迁移率。这里简单介绍一下制造双极应力刻蚀阻挡层的工艺流程。

(1)包括自对准硅化物形成在内的前续工艺;

(2)金属前通孔拉应力刻蚀阻挡层(氮化硅)沉积;

(3)去除PMOS器件区域的拉应力氮化硅;

(4)金属前通孔压应力刻蚀阻挡层(氮化硅)沉积;

(5)去除NMOS器件区域的压应力氮化硅;

(6)金属前绝缘层沉积及后续工序。

图5.13所示即为覆盖有双极应力刻蚀阻挡层的补偿式金属氧化物半导体场效应晶体管器件。如文献[29] 所述,通过采用双极应力刻蚀 阻挡层,NMOS和PMOS器件的驱动电流都可以得到大幅提升,提升幅度与薄膜厚度和应力大小的乘积成正向相关,甚至可以高达30% [29] (见图5.14)。

图5.13 双极应力刻蚀阻挡层的补偿式金属氧化物半导体场效应晶体管器件示意图

图5.14 双极应力对于NMOS和PMOS器件驱动电流的影响

在等离子体增强化学气相沉积工艺中,硅烷和氨气可以分别提供硅原子和氮原子,形成氮化硅薄膜,这种薄膜的组分除了含有硅和氮之外,还不可避免地被掺入一些氢离子。

初期人们只是通过气体流量和反应电压来调节氢含量和应力类型及其大小,而当半导体工艺对于氮化硅薄膜的应力要求越来越高时,紫外光照射工艺被引进,可以打断氮化硅中原有的硅氢键和氮氢键,形成更强的硅氮键。在紫外 光照射工艺的激发下,氮化硅的拉应力最高可以达到1.8GPa左右。

但紫外光照射工艺也会带来风险,这种沉积后处理工艺会使氮化硅薄膜体积产生收缩,如果薄膜所覆盖的器件或沟槽有较大的凸起,则容易在该处形成裂缝。一旦薄膜出现裂缝,应力松弛效应将会占据主导地位,应力作用将无法转移到半导体器件沟道。为避免裂缝的出现,通常会采用“沉积-紫外光照射”多次循环的制造工艺,来减小风险。而如果要形成压应力性质的氮化硅薄膜,通常会采用双频射频电源的等离子增强气相沉积技术。

高频射频电源通常用来解离反应气体,形成反应粒子源,而低频电源由于可以使得带电基团有更大的自由程, 通常可以产生更好的轰击效应,从而使得薄膜更为致密,并形成较大的压应力。引入质量较轻的氢气和重型粒子(如氩气和氮气)共同作用,并优化其他工艺参数,最高可以得到3.0GPa以上的压应力。

5.5 应力效应提升技术从上面几节中,我们可以看到应力效应不仅可以用来提高NMOS器件性能,而且也可以用来提高PMOS器件性能。除此之外,还有许多报道使用应力效应提升技术来更进一步地提高器件性能的方法。本节将介绍应力效应提升技术中的两个:

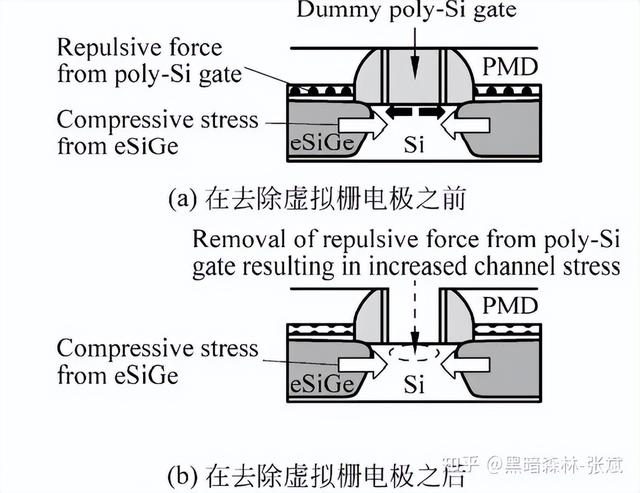

一个是通过去除虚拟栅电极的方法来提高嵌入式锗化硅所产生的压应力;

另一个方法是通过部分去除侧墙以使得双极应力刻蚀阻挡层薄膜更加接近沟道,从而提高应力效果。

在一个具有嵌入式锗化硅的PMOS器件中,如果它的栅电极采用大马士革结构方式制造的话,通过去除该虚拟栅电极的方法,沟道中的压应力可以得到显著提高。去除该虚拟栅电极后,它释放了原来从栅极带来的排斥力,从而使得嵌入式锗化硅增强了横向作用于沟道的压应力。这个应力效果提升技术可以获得更高的沟道应变和空穴迁移率,它的作用机理可以参考图5.15

图5.15 通过去除虚拟栅电极的方法来提高沟道中压应力的示意图

在去除虚拟栅电极后,可以在栅电极处的凹槽部位填充多晶硅或金属栅。不管其中的任何一个方法,去除虚拟栅电极后所提高的应力都在最后的器件中保留了下来。通过把大马士革多晶硅栅结构的形成与嵌入式锗化硅相结合的办法,可以获得如文献[38] 中所提到的好处。当使用嵌入式锗化硅时,可以提高大马士革结构的驱动电流。而没有使用嵌入式锗化硅的情况下,就没有办法提高驱动电流了。

在高介电常数栅和金属电极的整合结构中,有两个互相竞争的方法:金属栅极置前和金属栅极置后。在栅极置后工艺中,包含了虚拟栅的去除。当我们把它和嵌入式锗化硅工艺相结合,PMOS器件的性能在栅极置后的整合流程中,可以获得一个主要的优势就是:可以提高大马士革多晶硅栅结构形成后带来的应力效果。当我们决定栅极置 前和栅极置后哪种工艺用来整合进入高介电常数栅和金属电极的工艺流程中,这是一个主要的考虑因素。下面是一个把嵌入式锗化硅工艺和金属栅极置后工艺相结合的整合流程的简单例子。

(1)包括源/漏扩散区浅结形成工艺在内的前续工艺。

(2)源/漏区的硅衬底刻蚀工艺。

(3)在源/漏区选择性外延生长锗化硅。

(4)源/漏结的形成。

(5)自对准硅化物的形成。

(6)双极应力刻蚀阻挡层薄膜的形成。

(7)沉积金属层前的介电层。

(8)使用化学机械研磨去除上述介电层来暴露多晶硅栅电极。

(9)去除虚拟多晶硅栅电极和栅氧化物。

(10)沉积高介电常数栅和金属电极。

(11)使用化学机械研磨去除多余的金属层等后续工艺。

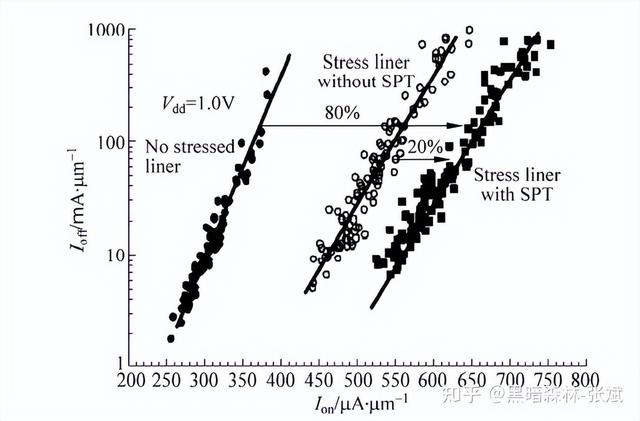

在5.4节已经讨论了双极应力刻蚀阻挡层薄膜在提高器件性能方面 的实用性。在应力薄膜技术中,器件性能的提高依赖于薄膜本身的应 力、厚度,并与沟道的接近程度有关。我们把应力薄膜放置于更加靠 近沟道的方法叫做应力临近技术(Stress Proximity Technique,SPT 。应力临近技术已经被成功地用于双极应力刻蚀阻挡层薄膜技术 中,它通过去除应力薄膜和多晶硅栅之间的侧墙,使得从应力薄膜到 沟道之间的应力接近和应变转移得到最大化 。要获得更高的器件性能,需要在沟道中施加更大的应变;也可以在同样应力的薄膜条 件下,通过减薄侧墙宽度来获得。然而,减薄侧墙宽度会降低器件的 短沟道特性,也会使自对准硅化物太靠近沟道,从而带来自对准硅化 物与沟道连通的风险。采用应力临近技术,侧墙在自对准硅化合物形成后去除,然后沉积双极应力刻蚀阻挡薄膜。这样就可以最小化上面 所提及的潜在问题。一个典型的应力临近技术工艺流程如下:

(1)包括自对准硅化物形成在内的前续工艺。

(2)通过干法刻蚀来部分去除侧墙。

(3)沉积拉应力薄膜。

(4)去除PMOS区的拉应力薄膜。

(5)沉积压应力薄膜。

(6)去除NMOS区的压应力薄膜。

(7)包含沉积金属前介电薄膜在内的后续工艺。

在部分去除侧墙工艺的过程中,需要小心处理并且防止过量损失自对准硅化物。从图5.16中可以看到,采用应力临近技术进一步地提高了器件的驱动电流。

图5.16 有和没有应力临近技术的PMOS驱动电流比较

除了提高驱动电流外,应力临近技术也有利于后续金属前的介电层的填洞能力,这是因为应力临近技术增加了填洞的宽度。